�@�@���ړ��y�[�W�ւ̗��K�҂�

�@�@���ړ��y�[�W�ւ̗��K�҂�

�@�@�@�}�� �X�}�z��ROM��RAM�̊W/�Ⴂ/���� �@�@�@�}�� �X�}�z��ROM��RAM�̊W/�Ⴂ/���� |

||||

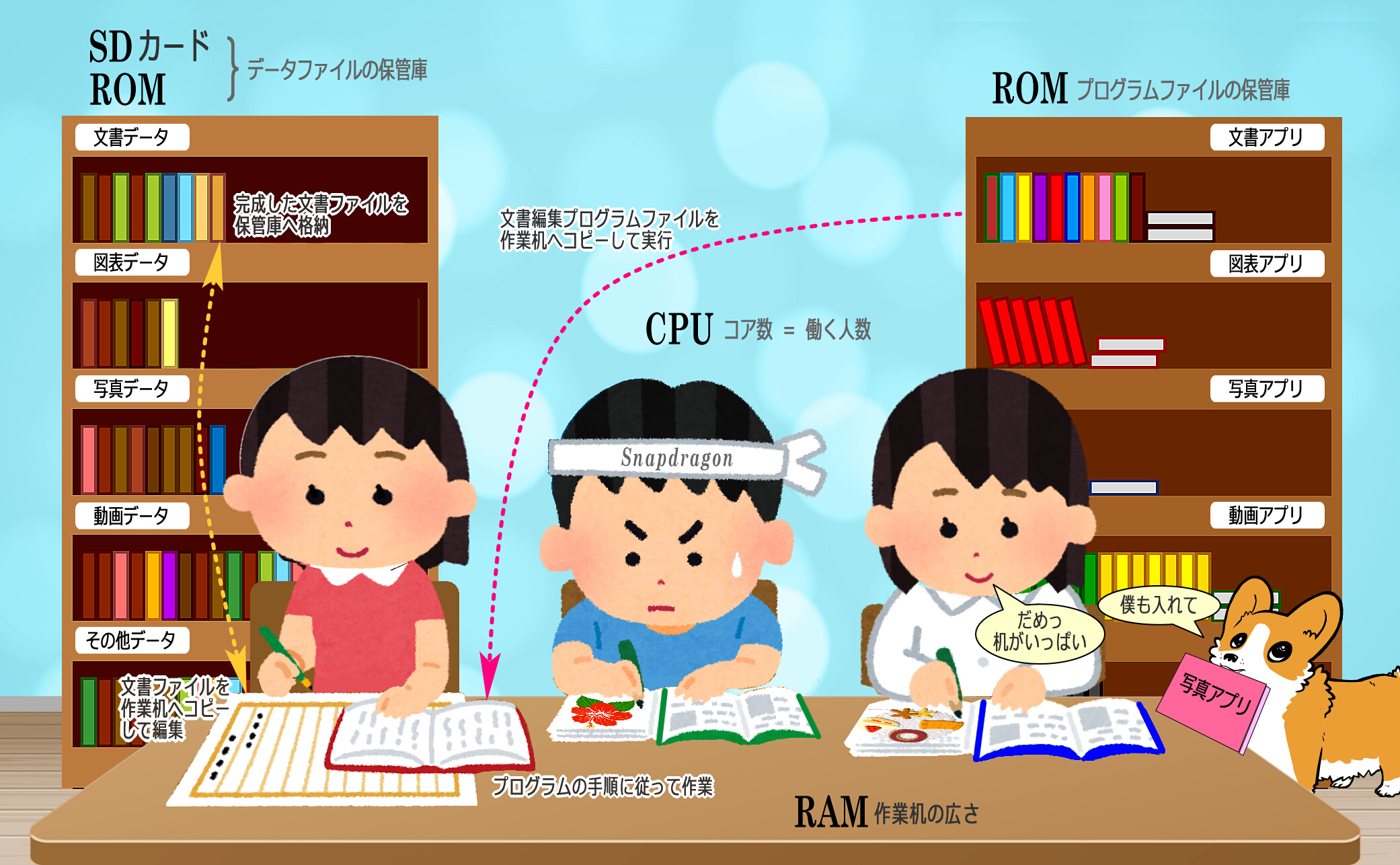

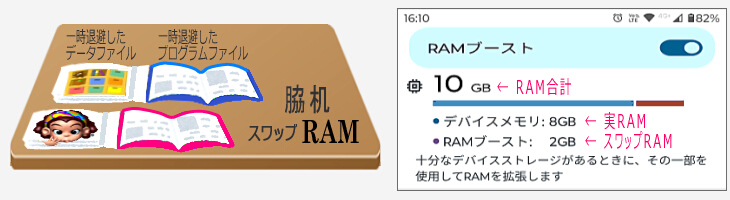

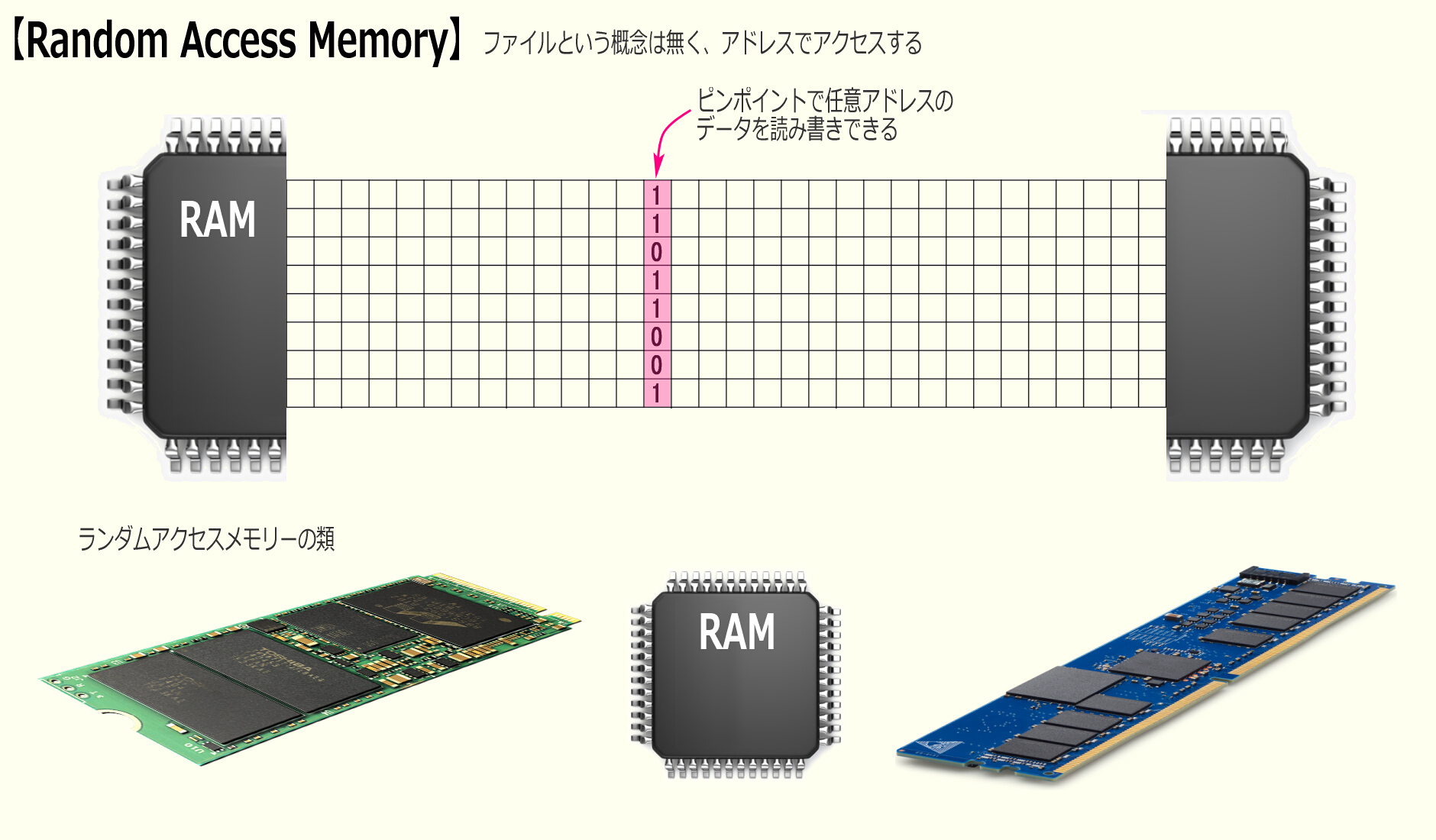

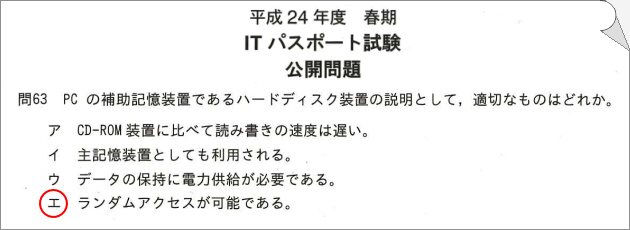

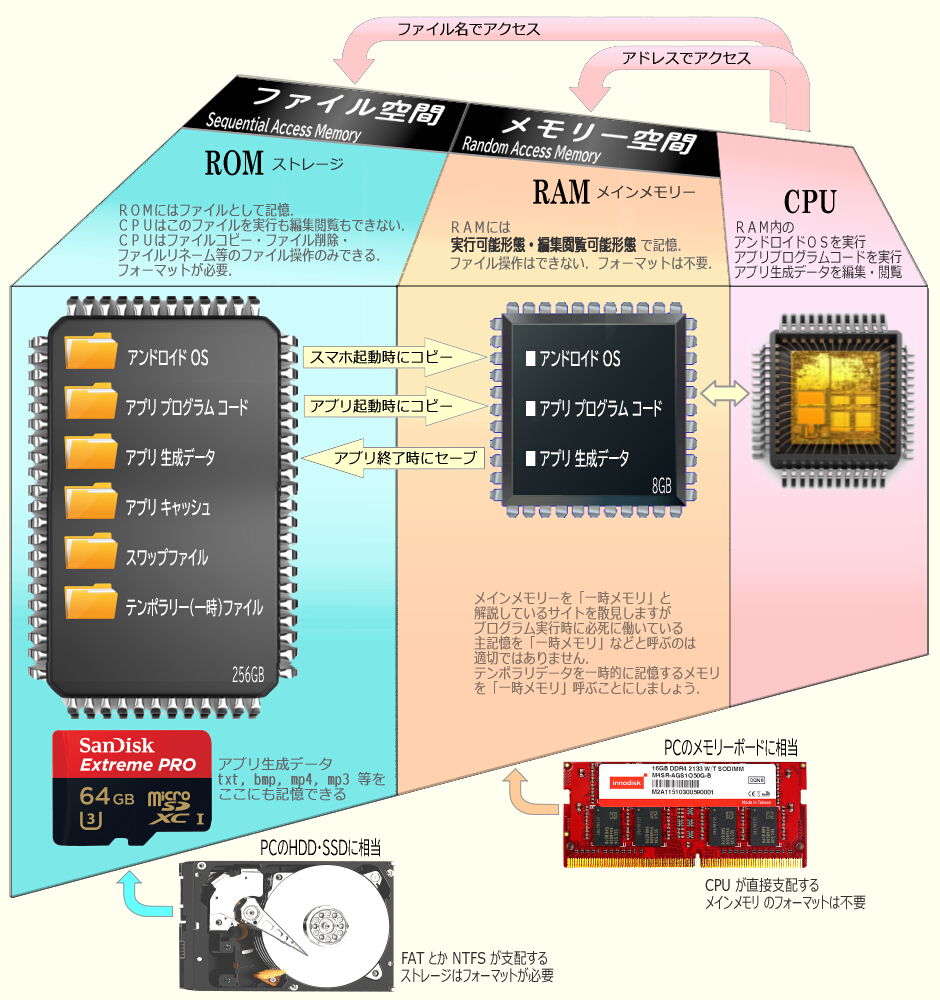

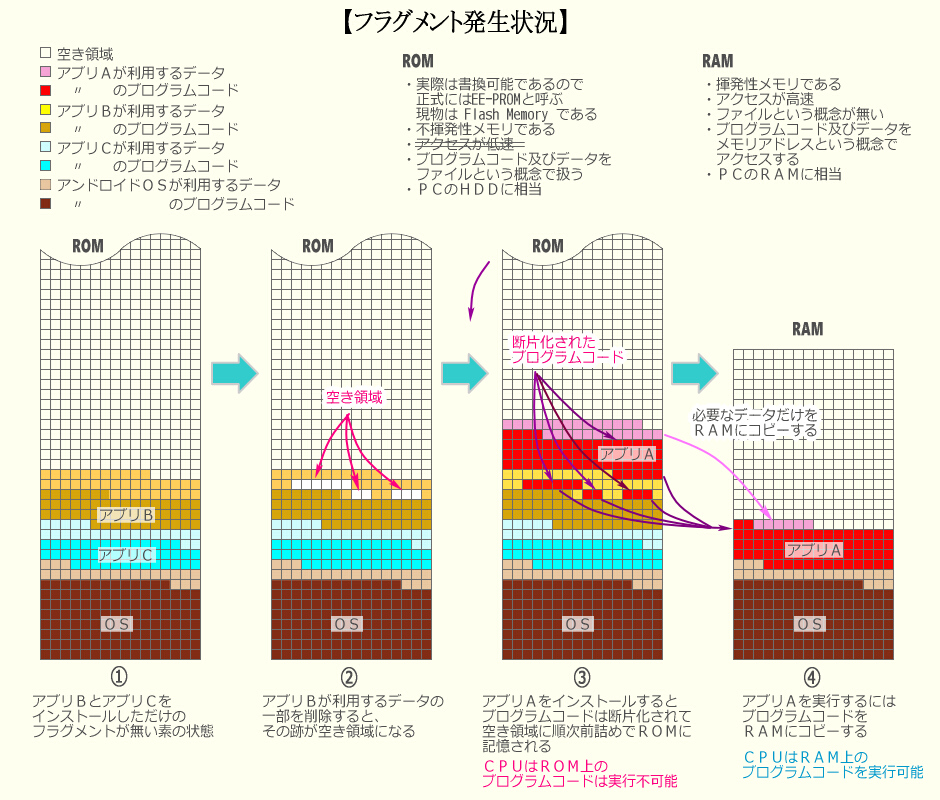

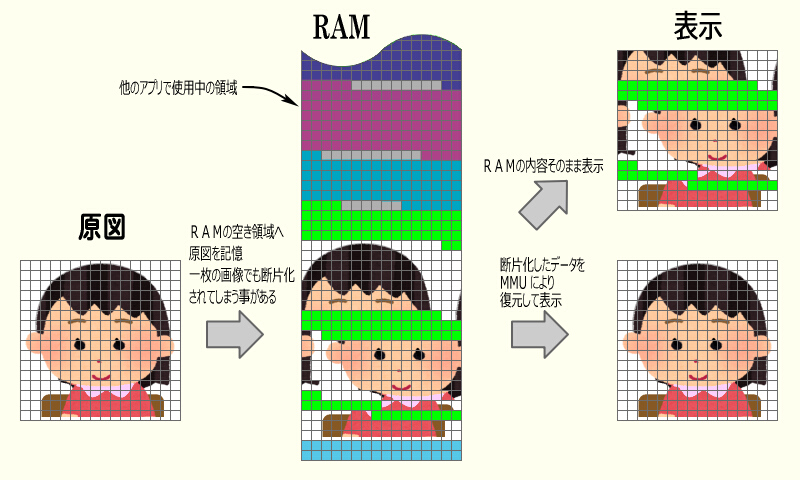

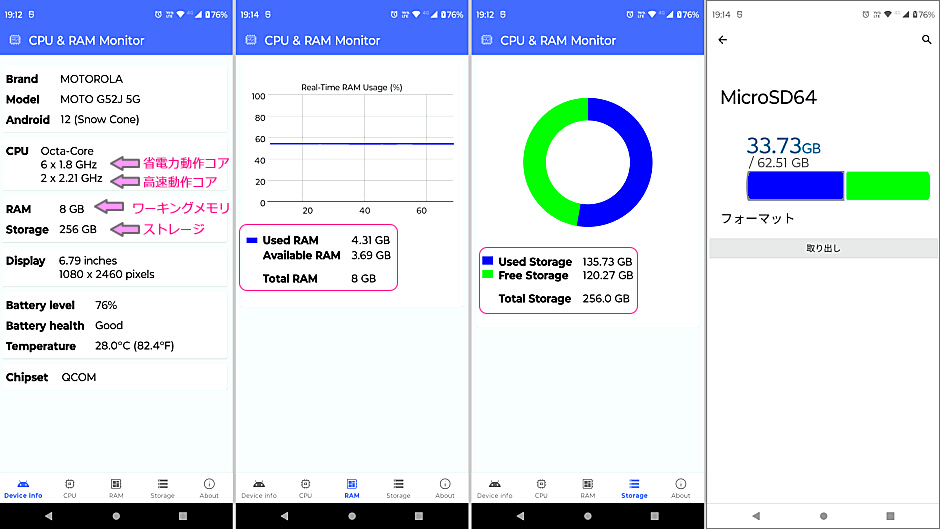

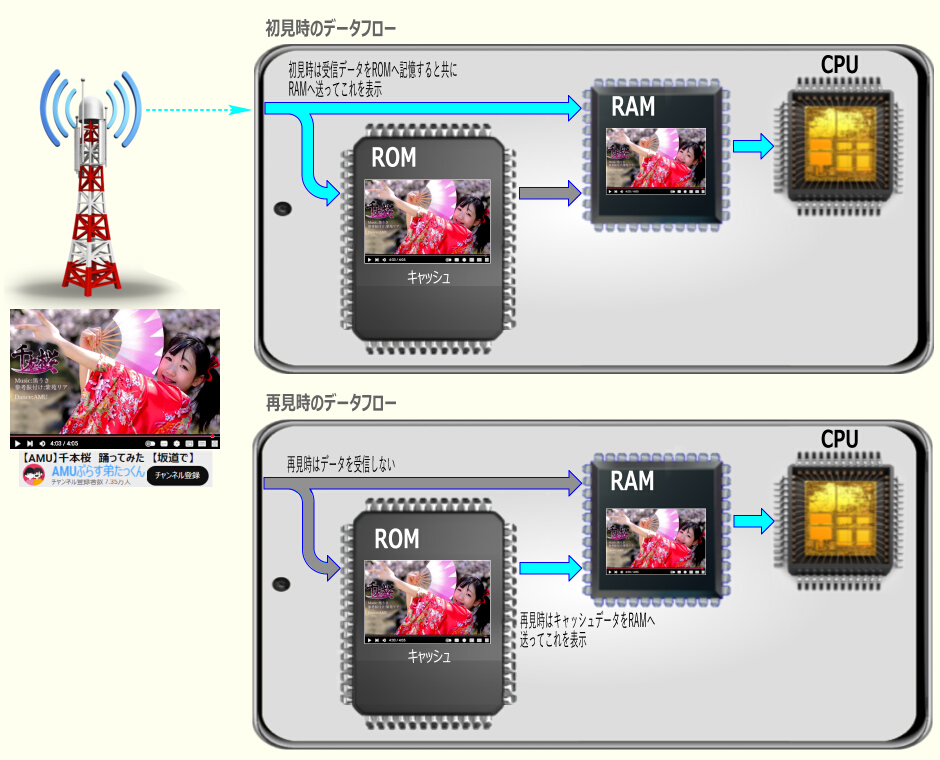

�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�i�C���X�g���u���킢���t���[�f�� ���炷�Ƃ�v����艇�p�@Thanks !�j ���@�X�}�z�� �@�@�b�o�t �̃R�A�͓����l�ɗႦ���܂��B �@�@�q�n�l �̓f�[�^�t�@�C���y�уv���O�����t�@�C���̕ۊnjɂɗႦ���A �@�@�q�n�l ����e�ʂł���Α����̃A�v���v���O�����t�@�C���Ƒ����̃f�[�^�t�@�C�����L�����邱�Ƃ��ł��܂��B �@�@�q�n�l �ƌď̂��Ă���ɂ��S�炸�A�f�[�^�t�@�C���ƃv���O�����t�@�C���͐��������������Ă��܂��B �@�@�q�`�l �͍�Ɗ��ɗႦ���A �@�@�q�`�l ����e�ʂł���Γ����ɑ����̃t�@�C�����J�����Ƃ��ł��܂��B �@�@�q�`�l �����e�ʂ̏ꍇ�́A �@�@�@�@�@�@�@�@�@�@�Ǐ�P�F�A�v���̋N���Ɉٗl�Ȏ��Ԃ������� �@�@�@�@�@�@�@�@�@�@�Ǐ�Q�F�A�v���̎��s�Ɉٗl�Ȏ��Ԃ������� �@�@�@�@�@�@�@�@�@�@�Ǐ�R�F�f�[�^�t�@�C�����J���܂łɈٗl�Ȏ��Ԃ������� �@�@�@�@�@�@�@�@�@�@�Ǐ�S�F�u���̃A�v���͉������Ă��܂���v�u�I������^�ҋ@����v�̏�ԂɂȂ��Ă��܂� �@�@�@�@�@�@�@�@�@�@�Ǐ�T�F�X�}�z���t���[�Y���Ė������ɂȂ��Ă��܂� �@�@�@�@�@�@�@�@�@�@�Ǐ�U�F�ň� �n�r ���V���b�g�_�E�����Ă��܂� �@�@�����Ō�������� �q�`�l �𑽂����邽�߂ɘe����ݒu���܂��B �@�@�Ⴆ�Έ����ƒ��Ɋ����ݍ�Ƃ��������ꍇ�́A��Ɠr���̃f�[�^�t�@�C���ƃv���O�����t�@�C����ۊnjɂ֖߂��̂ł͂Ȃ��A �@�@��Ɠr���̃t�@�C����e���ֈꎞ�ޔ����č�Ɗ����܂��B �@�@�����ݍ�ƏI����A�ꎞ�ޔ�������Ɠr���̃t�@�C����e�������Ɗ��֕��A���Ē��f���ꂽ��Ƃs���܂��B �@�@�@�@�@�@�@�@�@�@  �@�@���̘e�����X���b�v�q�`�l (�X���b�v������)�ƌĂт܂��B�X���b�v�q�`�l�͂q�n�l�̈ꕔ��q���ė��p���܂��B �@�@Motorola �Ђł͂��̎d�g�݂��q�`�l�u�[�X�g�ƌĂ�ł��܂��B �@�@�X���b�v�q�`�l�ֈꎞ�ޔ����ꂽ�f�[�^�t�@�C���ƃv���O�����t�@�C���͉{���E�ҏW�����s���ł��܂��A �@�@�^�X�N�L�� (�A�v���I��) ������Ƃ̑��s���X���[�Y�ɐi�ނƂ��������b�g������܂��B �@�@�b�o�t�̃R�A����������Γ����ɕ����̃A�v�����X���[�Y�Ɏ��s�ł��܂��B �@�@��ɂP�R�A���P�^�X�N�S����̂ł͂Ȃ��A�ɂ��P�R�A�������^�X�N�S������A �@�@�P�^�X�N�������R�A���ғ������邱�Ƃ�����܂��B �@�@�b�o�t�̃R�A�ւ̃N���b�N���g���������ȂقǓ����l�̏������x�������Ȃ�܂��B �@�@�A���������x�Ə���d�͂Ƃ̓g���[�h�I�t�̊W�ɂ���̂ŁA�����X�}�z�̓R�A���g�������Ă��܂��B �@�@�f�[�^�t�@�C���ƃv���O�����t�@�C���͕ۊnjɂ��猴�{�������o���̂ł͂Ȃ��A�R�s�[���Ƃ��Ăq�`�l�ɒu���܂��B �@�@���̂悤�ɂ���ƈ���A�v�������ɊJ���Ă���f�[�^�t�@�C���Ƃ��v���O�����t�@�C�����A�ʂ̃A�v���������ɊJ�����Ƃ��ł��܂��B �@�@�ȏ�͍J�ŗǂ�����������ł����A�d�g�݂̖{�������ɋL���܂��B  ���@�悸�A�q�`�l (Randam Access Memory) �̐����ł��B �@�@�t�@�C���Ƃ����T�O�͖����A�A�h���X�ŃA�N�Z�X���܂��B �@�@�q�`�l �͂b�o�t�����ڂɃA�h���X���w�肵�ăs���|�C���g�ŃA�N�Z�X�ł��܂��B �@�@�q�`�l �͊������������[�ł��̂ŃX�}�z�̓d�����Ɠ��e�͕ێ�����܂���B �@�@�q�`�l ���Ńt���O�����g���������Ă��y�[�W�P�ʂł���A �@�@�l�l�t(Memory Management Unit) �̘_��(���z)�A�h���X�������A�h���X�ϊ��ɂ�萳�����A�N�Z�X�ł��܂��B �@�@�b�o�t�͂q�`�l�ɋL�����ꂽ�A�v���̃v���O�����R�[�h�����s�ł��A�A�v�������������f�[�^���{���E�ҏW�ł��܂��B  ���@���ɁA�q�n�l (Read Only Memory) �̐����ł��B�@�@�@�@�@�@�@�@�@�@�@(�C���X�g�� https://www.pngwing.com/ja ��艇�p) �@�@�����_���A�N�Z�X�\�ȃ������[�ł����Ă��X�}�z���̂q�n�l�Ƃ��o�b���̂q�`�l�f�B�X�N�̔@�� �@�@�t�e�r(Universal Flash Storage)���̃t�@�C���V�X�e���x�z���ɒu�����Ƃr�`�l(Sequential Access Memory) �Ƃ��ē��삵�܂��B �@�@�r�`�l�̓A�h���X�Ƃ����T�O�͖����t�@�C�����ŃA�N�Z�X���܂��B �@�@�r�`�l�͂b�o�t�����ڂɃA�h���X���w�肵�ăs���|�C���g�ŃA�N�Z�X�ł��܂���B �@�@�r�`�l�̓t�@�C���V�X�e���̓����㐏���Ƀt���O�����g���������܂��B �@�@�r�`�l�̓t�@�C���V�X�e���̎x�z���ɂ����Ăl�l�t(Memory Management Unit) �̌��͂��y�Ȃ��̂ŁA �@�@�b�o�t�͂r�`�l�ɋL�����ꂽ�A�v���̃v���O�����R�[�h�����s�ł����A�A�v�������������f�[�^���{���E�ҏW���ł��܂���B �@�@�@�@�@�@�@�@���@�����_���A�N�Z�X�ƃV�[�P���V�����A�N�Z�X�̔����ȂƂ��� �@�@�@�@�@�@�@�@  �@�@�@�@�@�@�@�@���@�A���A�u�h�s�p�X�|�[�g�����v�ł͂g�c�c�́u�����_���A�N�Z�X���\�v�������Ȃ��Ă��܂��B �@�@�@�@�@�@�@�@�@�@�����_���A�N�Z�X�ƃV�[�P���V�����A�N�Z�X�̗p��̒�`�͏ɂ�肩�Ȃ�B���ȂƂ��낪����܂��B �@�@�@�@�@�@�@�@�@�@�P�F�V�i�̂g�c�c�փt�@�C�����L�^����ƃN���X�^�[�͘A�����Ă���̂ŁA �@�@�@�@�@�@�@�@�@�@�@�@�@�@���̃t�@�C����ǂގ��̓V�[�P���V�����A�N�Z�X�ƂȂ�A �@�@�@�@�@�@�@�@�@�@�@�@�@�@�g�����g�c�c�փt�@�C�����L�^����ƃN���X�^�[�͗��U���Ă���̂ŁA �@�@�@�@�@�@�@�@�@�@�@�@�@�@���̃t�@�C����ǂގ��̓����_���A�N�Z�X�ƂȂ�B �@�@�@�@�@�@�@�@�@�@�Q�F�N���X�^�ڂɎw��ł���̂ŁA�N���X�^�P�ʂŌ���ƃ����_���A�N�Z�X�ł���B �@�@�@�@�@�@�@�@�@�@�R�F�Z�N�^�[�ڂɎw��ł��Ȃ��̂ŁA�Z�N�^�[�P�ʂŌ���ƃV�[�P���V�����A�N�Z�X�ł���B �@�@�@�@�@�@�@�@�@�@�S�F�A�h���X�ڂɎw��ł��Ȃ��̂ŁA�o�C�g�P�ʂŌ���ƃV�[�P���V�����A�N�Z�X�ł���B �@�@�@�@�@�@�@�@�@�@�]���āA�����ɏo�肳�ꂽ�ꍇ�͏o��҂����҂��������̂��ǂ��ł��傤�B  ���@�q�n�l(�t�@�C�����)�Ƃq�`�l(�������[���)�Ƃb�o�t�̊W�̂܂Ƃ߁B �@�@�q�n�l���x�z�����t�e�r���̃t�@�C���V�X�e���͊����Ƃ����t�@�C����@���ɂq�n�l�ɔ[�߂邩�ɐ�O�������܂�A �@�@�����t�@�C���̎��s�\�`�ԂƂ��{���E�ҏW�{���\�`�Ԃ͕ێ�����܂���B �@�@�@�@�@�@�P�F�t�@�C���̒f�Љ��B �@�@�@�@�@�@�Q�F�t�@�C���V�X�e�����x�z����r�`�l (Sequential Access Memory) �� �@�@�@�@�@�@�@�@�@�@�b�o�t���s���|�C���g�Ŏw�肵���A�h���X�ڃA�N�Z�X�ł��܂���B �@�@���̏� MMU(Memory Management Unit) �̘_��(���z)�A�h���X�������A�h���X�ϊ��ł͑Ή��ł��܂���B �@�@�b�o�t�͂q�n�l�ɋL�����ꂽ�A�v���̃v���O�����R�[�h�����s�ł����A�A�v�������������f�[�^���{���E�ҏW���ł��܂���B �@�@�����t�@�C�������s�E�{���E�ҏW����ɂ͂b�o�t�����ڎx�z����q�`�l(�������[���)�փR�s�[���ė��p���܂��B �@�@�q�`�l ���Ńt���O�����g���������Ă��y�[�W�P�ʂł���A �@�@�l�l�t�̘_��(���z)�A�h���X�������A�h���X�ϊ��ɂ�萳�����A�N�Z�X�ł��܂��B �@�@�b�o�t�͂q�`�l�ɋL�����ꂽ�A�v���̃v���O�����R�[�h�����s�ł��A�@�A�v�������������f�[�^���{���E�ҏW�ł��܂��B �@�@���ꂪ�q�n�l(�X�g���[�W)�Ƃq�`�l(���C��������)�����ݕ������Ė������S���鍪�{���R�ł��B ���@�����A�v�����^�[�Ƃ��f�W�J���Ƃ��d�q�s�A�m�Ƃ��̃X�^���h�A�����P�\�@�̏ꍇ �@�@�q�n�l��̃v���O�����R�[�h�͘A���Œ肵�Ă��āA�t�@�C����Ԃł͂Ȃ��������[��Ԃɔz�u�����̂� �@�@�b�o�t�� �q�n�l��̃v���O�����R�[�h�ړǍ���Ŗ��߂����s�ł��܂��B �@�@�q�n�l����q�`�l �փR�s�[���Ă��痘�p����Ƃ������ʂȏ����͂��܂���B  ���@�f�Љ��̔����̖͎��}�ł��B �@�@�X�}�z�̂q�n�l�͂o�b�̂g�c�c�ɑ������܂��B�����s�������������[�ł��B �@�@���{�ł͂q�n�l�ƌď̂��Ă��܂������E�W���� Internal Memory Storage (�����X�g���[�W)�ł��B �@�@�X�}�z�̂q�n�l���ɂ̓v���O�����R�[�h�ƃf�[�^ (����.txt�E�摜.bmp�E����.mp4�E���y.mp3 ��) �������O�l�߂ŋL������܂��B �@�@�w�������͌��ԂȂ���{�̃t�@�C�����ɘA�����ċL������Ă��܂����A �A�@�v���O�����t�@�C�����̓f�[�^�t�@�C��(e.g. �摜�t�@�C��)�̍폜�E�ҏW��������ƌ��L�����ꏊ�͋̈�ɂȂ�܂��B �@�@������J��Ԃ��Ƃq�n�l���ɒ��H���̂悤�ȋ̈悪�����������܂��B �B�@���̒��H����Ԃ̂q�n�l�ɐV�����t�@�C���������Ƌ̈�߂�悤�ɏ����O�l�߂ŋL������܂��B �@�@���̌��ʏ����܂ꂽ��{�̃t�@�C���͘A�����Ă��Ȃ��f�Љ�(�t���O�����g)��Ԃł��B �@�@�q�n�l���ł�MMU�̘_��(���z)�A�h���X�������A�h���X�ϊ��őΉ��ł��܂���B �C�@�����ŁA�A�v���`���N������Ƃq�n�l���̒f�Љ����ꂽ�v���O�����R�[�h�� �@�@�{���E�ҏW�Ώۂ̃f�[�^(.txt .bmp .doc .mp4 .mp3 ���t�@�C��)���e�X�q�`�l�փR�s�[���܂��B �@�@���̎��q�`�l���ł��f�Љ����N���蓾�܂��� �@�@�q�`�l���ł�MMU(Memory Management Unit) �̘_��(���z)�A�h���X�������A�h���X�ϊ��őΉ��ł��܂��B �@�@�A���A�����������̒f�Љ��̓y�[�W�P�ʂȂ�� MMU�̘_��(���z)�A�h���X�������A�h���X�ϊ��� �@�@�z���ł��܂����A�y�[�W���ł̒f�Љ���MMU�ł͑Ή��ł��܂���B  ���@�摜�f�[�^�̒f�Љ��ƕ����i�l�l�t���@�\���Ȃ��ꍇ�̖͎��}�j

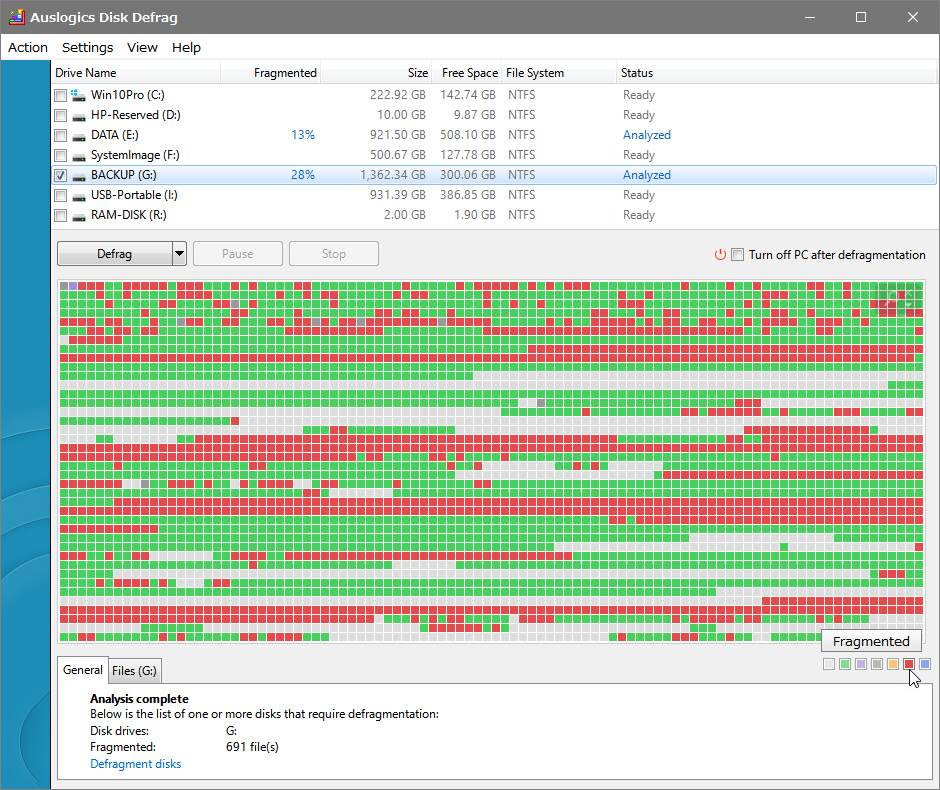

���@�Q�l�Ƃ��āA�o�b�̂g�c�c�̒f�Љ�(�t���O�����g)�̗l�q�ł��B �@�@�t���O�����g�Ƃ͒f�Љ������N���X�^�Ƀt���O��(��)�𗧂Ă邱�Ƃł��B �@�@�t���O�������Ă���N���X�^�ɂ͗��ꂽ�ʒu�ɘA�������N���X�^���L��Ƃ����ڈ�ł��B �@�@�f�t���O�����g�Ƃ͊��̗����Ă���N���X�^���W�߂Ĉ��̘A��������Ԃɂ��邱�Ƃł��B �@�@�A��������ԂɂȂ�Ɗ����~�낵�܂��B �@�@�����̃f�t���O�����g�\�t�g�E�F�A�͓����ɃK�x�[�W�R���N�V���������s����܂��B �@�@1000GB �̂g�c�c���f�t���O�����g����ɂ͖�30��������܂��B  ���u�L���b�V���v�̎v�z�B�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@(�C���X�g�� https://www.pngwing.com/ja ��艇�p) �@�@Cache �͌��������܂��� �@�@Cash�@�͌������̂���  ���@YouTube �������ƍČ����̃f�[�^�t���[�ł��B �@�@�ʏ�̓L���b�V���̓ǂݏ����̓o�b�N�O���E���h�ňÖٓI�ɍs���܂����A �@�@�d�g�̓͂��Ȃ��R�̒��ł��g����o�R�n�} GPS�A�v���uYAMAP�v�ł͖����I�ɃL���b�V�����삪�s���܂��B �@�@���C�ǂ��e��ł��� AMU ����������ɂȂ�܂� ���yAMU�z��{�� �x���Ă݂��y�⓹�Łz |

||||

�@�X�}�z�̃N���b�N��x������Ə���d�͂����闝�R �@�X�}�z�̃N���b�N��x������Ə���d�͂����闝�R |

||||

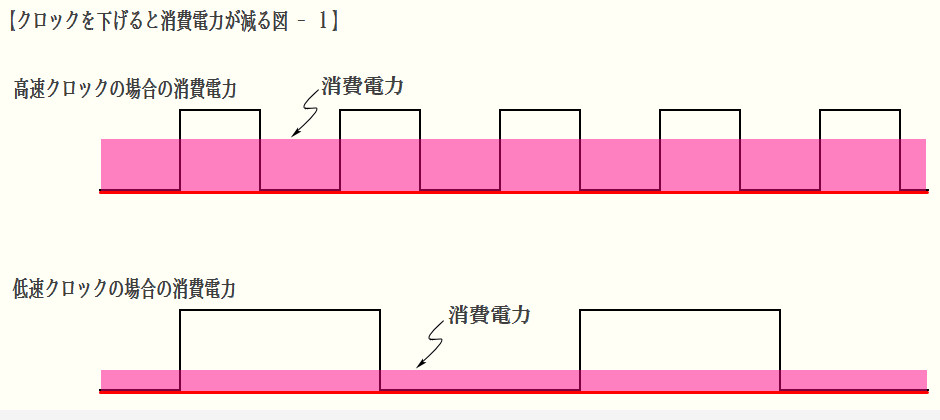

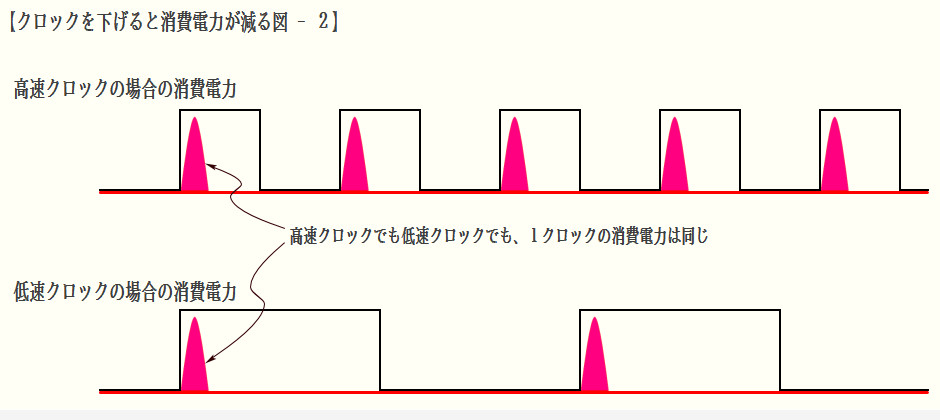

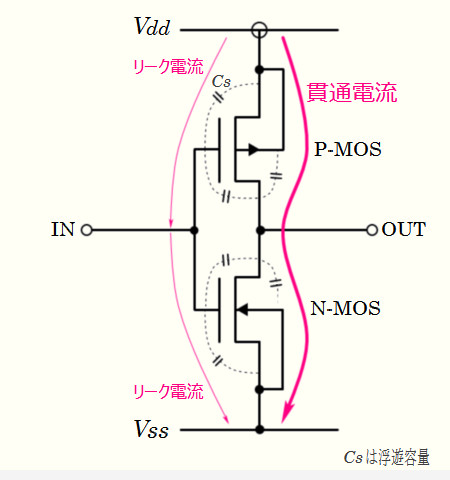

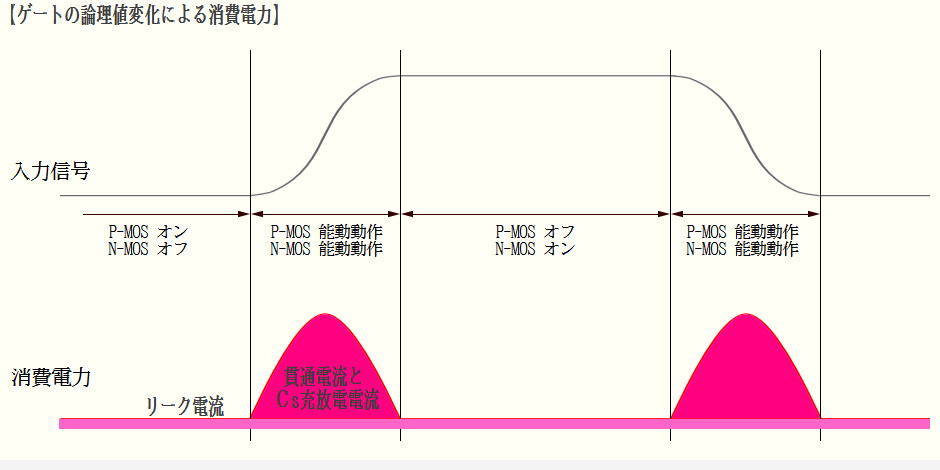

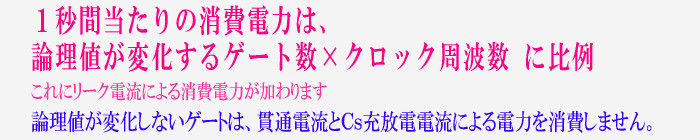

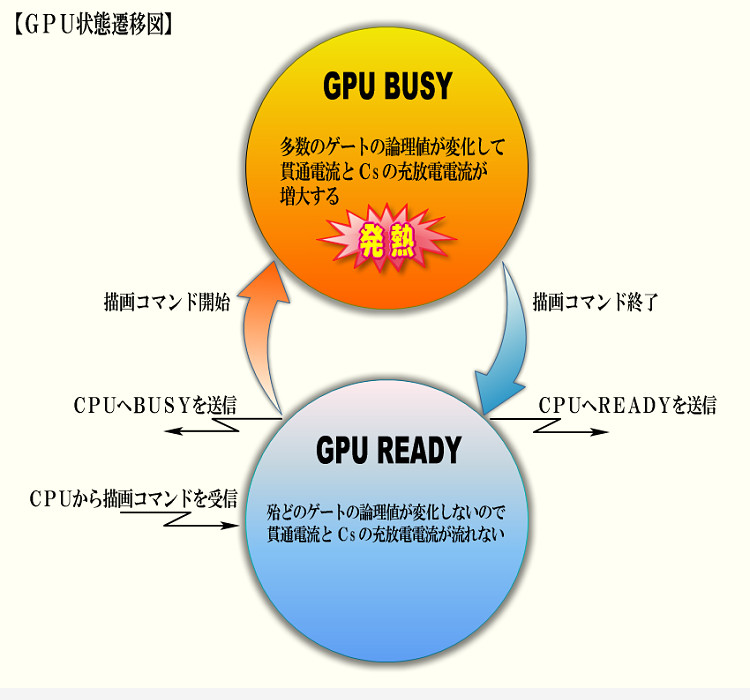

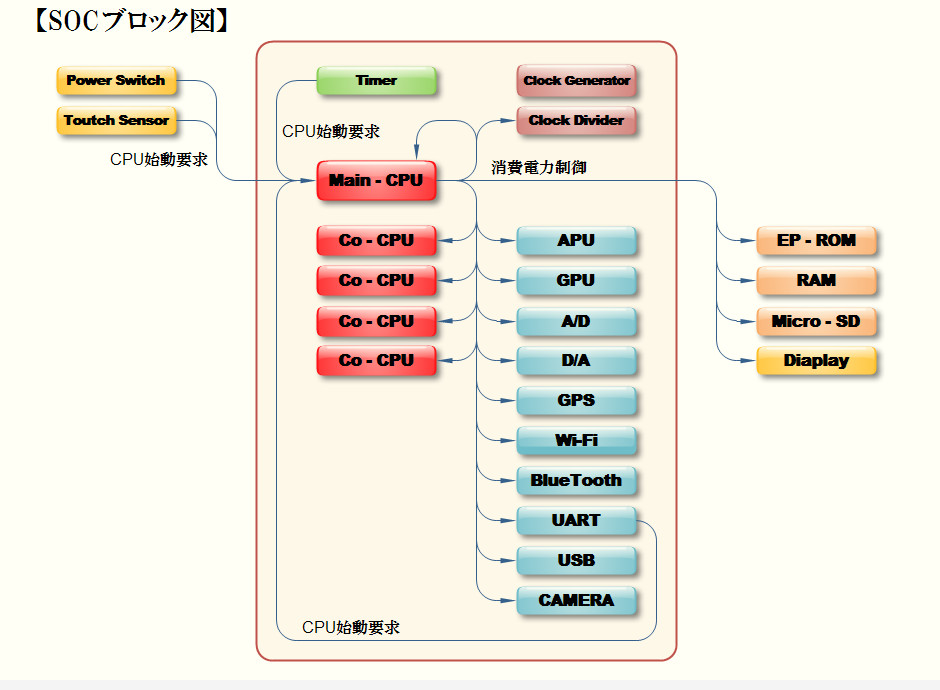

���@�J�ŗǂ������Ă����g�N���b�N��ᑬ�ɂ���Ə���d�͂���������h�Ƃ���������}���������̂ł��B �E�@�m���ɒᑬ�N���b�N�ł͏���d�͂��������Ă���̂͂킩��܂����A �@�@�c�O�Ȃ���A�ǂ����ď���d�͂��������邩�̐����ɂ͐����Ă��܂���B �E�@�J�ŗǂ������Ă����g�����ׁh�Ƃ��g�ᕉ�ׁh�Ƃ����Ӗ����A���̐}����ł͎ߑR�Ƃ��܂���B  ���@�P���N���b�N�̗����G�b�W�����^�f�W�^���V�X�e���̏���d�͂̂悤���ł��B �E�@�N���b�N�����^�V�X�e���̏ꍇ�́A�N���b�N�̗����G�b�W�ŏu�ԓI�ɓd�͂�����܂��B �E�@�ᑬ�N���b�N�̏ꍇ�̓N���b�N�̗����G�b�W�̕p�x����������̂ŁA���ʓI�ɓd�͂������p�x���������܂��B �E�@���̐}�Ȃ�Βᑬ�N���b�N�ŏ���d�͂���������������t���܂��B�g�Ⴉ���������h���Ƃł��傤�B �E�@�ǂ����ăN���b�N�̗����G�b�W�ŏu�ԓI�ɓd�͂������̂������̐}�Ő������܂��B  ���@�ł��V���v���� NOT �Q�[�g�ł��B �E�@���̉�H�Ɏ��̎O�̏��]���Ȃ��d��������܂��B �@�@(1) �o�|�l�n�r�Ƃm�|�l�n�r���ђʂ���d���i���̉��̐}�Ő������܂��j �@�@(2) �b���i���V�e�ʁj���[�d�^���d����d�� �@�@(3) ���[�N�d���i���I�ɗ����R��d���j  ���@�Q�[�g�̓��͘_���l���ω����鎞�ɗ����ђʓd���Ƃb���[���d�d���̐����}�B �E�@�Q�[�g�̘_���l�����S�Ɂg�O�h�܂��́g�P�h�̏ꍇ�́A �@�@�Б��̂l�n�r�͊��S�ɂn�m��ԂŁA�ʂ̂l�n�r�͊��S�ɂn�e�e��Ԃł��B �@�@�l�n�r�����S�ɃI���܂��̓I�t�̏ꍇ�͓d�͂�����܂���B �@�@�������A���ȃ��[�N�d���ɂ��d�͏���͂���܂��B �E�@�Q�[�g�̘_���l���g�O�h�܂��́g�P�h�łȂ��ߓn��Ԃ̏ꍇ�́A �@�@�����̂l�n�r���\�������ԂɂȂ��Ă��܂��܂��B�f�W�^������ł͂Ȃ��A�i���O����ł��B �@�@���̎��Ɋђʓd��������Ă��܂��܂��B �@�@���J�X�C�b�`�ɗႦ����u���C�N �r�t�H�A �u���[�N�v���ł��B �E�@�����ɂb���i���V�e�ʁj�̏[���d�d��������܂��B �E�@�ȏ�̂��Ƃ���A   ���@����d�͌v�Z�̃I�[�\�h�b�N�X�Ȍ������ł��B �@�@�J���g�P�b�Ԃ̃N���b�N��[������]�h���g���g��[/SEC]�h�ŕ\�L����Ă���v�Z�����U�����܂����A �@�@���̂悤�Ȏ��̉E�ӂ͍��ӂ̃f�B�����W����[W]��[J/S]�ƍ��v���܂���B �@�@�������ɂ����ĉE�ӂƍ��ӂ̃f�B�����W�������Ⴄ���́A�����d�v�ȗv�f���������Ă���\��������܂��B �@�@�܂��A�f�B�����W�����̈Ⴄ�ʂ̏揜�Z�͂ł��܂��������Z�͂ł��܂���B �@�@�Ⴆ�l�j�r�n�ɂ����� �Q[Kg]�{�R[�l]���H �̂悤�ȉ��Z�͂ł��܂���B �@�g���g��[/SEC]�h�ŕ\���ꂽ�X���ł��v�Z�͂ł��܂����A�������ۂ̖{���𗝉����邽�߂ɂ͌�������p���܂��傤�B  ���@�f�o�t�iGraphics Processing Unit�j�̂a�t�r�x�^�q�d�`�c�x�̏�ԑJ�ڐ}�ł��B �E�@�O���t�B�b�N���Z�̂��߂ɂP�N���b�N�Őς�������p��������Z��Ȃǂ��t���ғ�������ƁA �@�@�c��Ȑ��̃Q�[�g�Ř_���l�ω����N���ď���d�͂����債�܂��B �@�g�����ׁh�Ƃ��g���ғ����h�Ƃ́A���̂悤�ȏ�Ԃ��w���܂��B  ���@�r�n�b�iSystem On a Chip�j�̃u���b�N�_�C�A�O�����̈��ł��B �E�@����d�͐���́A��~������u���b�N�ւ̃N���b�N�̋������~����B�E�E�E�E�E�@�ђʓd����ጸ�̂��� �@�@�@�@�V�@�@�@�@�@�@�@�@�@�V�@�@�@�@�@�@�d�͂̋������~����B�E�E�E�E�E�E�E�@���[�N�d���ጸ�̂��� �E�@�l������ - �b�o�t ��������~�����Ă��܂����Ƃ��ł���r�n�b������܂��B ���@�]�k�ł����A���������8000�Q�[�g�K�͂̂k�r�h�x�[�V�b�N���W�b�N���s�s�k�����_�����W�b�N�œ��쌟�������Ƃ�����܂��B �@�@�����̔����̐����v���Z�X�̓T�u�~�N�����ȑO�̂P�ʃ��[���ł����B ���@Link�FLSI�̒����d�͐v�@���e�N�j�J�����r���[ PDF���� �@�@�@�@�@�����d��LSI����������SOI�f�o�C�X�Z�p ���e�N�j�J�����r���[ PDF���� �@�@�@�@�@�R���f���T����(�T)�@���v�Вc�@�l���{�d�C�Z�p�ҋ��� �@�@�@�@�@�X�}�[�g�t�H�����x����n�[�h�E�F�A�v���b�g�t�H�[���@�x�m��  |